|

||||||||||||||||

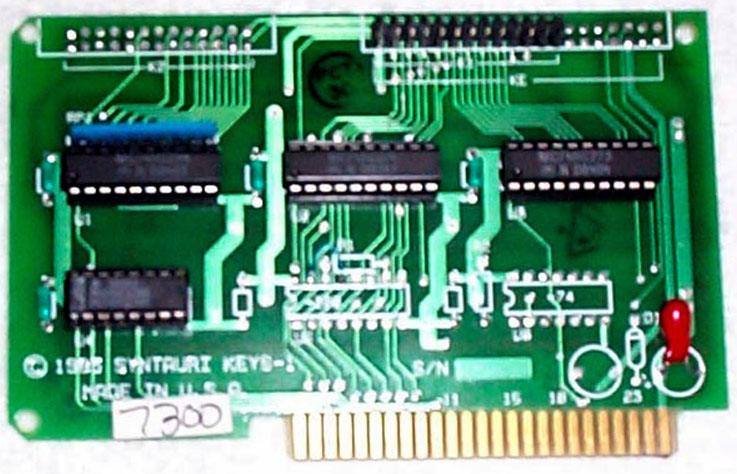

| the Apple II interface card of the alpha syntauri - later version | ||||||||||||||||

| The interface of the alpha syntauri in the

Apple II is rather simple due to the fact that it only passes over the

information from the internal decoder interface inside of the keyboard. Up to the moment it seems that one part of the information is a parallel set of the 8 Databits. And it seems that at the other hand some part of the information might be some kind of handshaking and probably some kind of Interrupt-handling. Unfortunatly this part of the information is not complete because the alpha syntauri system i have purchased from ebay did not have this interface card. The only information availiable, was taken from only 2 pictures that i had in former days.  At the beginning just a important remark: During the time of distribution of the alpha syntauri system, the system has changed several times with several revisions. The information provided here cover the most common more later ( but not last ) revision of the system I try to research also information on later and earlier revisions at the moment. The moment such information gets accessable, i will add such informations to the currently blank pages of this series of pages. Like with most topics i´ve recognized endurance to be one of the most powerfull skills...... The above

displayed bad picture of a damaged interface card was for more than 4

years the only info i had on the kind of interface. answering a big bunch of questions about details of this Interface card. |

||||||||||||||||

| The pictures

below have been made by Mr. Hobbs and display a working version of this

interface card with the small misfit that pin1 at the Connector K1 is broken and is to be repaired. I just enhanced the pictures a bit by correcting perspective and lighting. The left picture displays the component side while the right picture displays the same card at the soldering side. |

||||||||||||||||

|

||||||||||||||||

Unfortunatly after removal of the Chips it turned out that most sockets didn´t permit very well examination of the traces below of the sockets and that would have required a large amount of testing measurements to detect the correct connections. I was therefor very happy that Mr. Hobbs decided to desolder the sockets and send me a second set of pictures of the card with extracted sockets. This permitted me to recreate the entire shematic ( electronic circuit plan ) of this interface card. I also added this information to the documentation PDF-file at the end of this section so that in future everybody me be enabled to carry out repairs at the system and at this card. |

||||||||||||||||

|

||||||||||||||||

For identification of several components and details Mr. Hobbs has taken several more pictures that offered more details of the card. |

||||||||||||||||

|

||||||||||||||||

After i had the pictures i started working with Photoshop and converted colors to alter the pictures that way that at the end from both sides a kind of clean negativ film resulted for each side of the interface card and i used the blue color for traces at the component side of the interface card and red for the soldering side of the card. |

||||||||||||||||

|

Here is the data of the original card:

|

||||||||||||||||

|

||||||||||||||||

|

||||||||||||||||

|

In case of damage here are the informations needed for replacement of this card:

|

||||||||||||||||

|

||||||||||||||||

|

Mounting both layers together gave me a very clear impression of all the

connections at the interface and enabled me to recreate the entire

schematic. |

||||||||||||||||

|

||||||||||||||||

| From the

reverse engineered replacementcard above the PCB manufacturer files:

as zip-file: ASIFCGerber_mm.zip ( This files are used with measurement in Millimeter > mm ! )

as rar-file:

ASIFCGerber_mm.rar

( This files

are used with measurement in Millimeter > mm ! ) |

||||||||||||||||

|

||||||||||||||||

In ext part of this page are the function diagrams of the used chips and i sorted them in the same order they are placed at the interface card an i explain below the chips that are used at this card and the function they perform there at this card. While this order is given by the location on the card it does not order the the chips

by their given order in the explaination. then the 74LS273

in the top row at the right and followed at the end by the

74LS74 in the bottom row at the right side. |

||||||||||||||||

|

||||||||||||||||

|

||||||||||||||||

|

due to european laws

and german court decision: I hereby declare no responsibility to any "deep links" resulting from the links in this page. I have no influence to the pages linked hereby in this page and the contents in those pages. I therefor can´t take any kind of responsibility to contents in the pages, where these links direct the readers browser to nor to the contents resulting from following up links from those pages. The reference to contents by this links is dependent ro the status of the date when the links have been set ( April 2013 ) and it might occur that references and contents may change by the fact that domains may have been discontinued from their former owners. In such cases i can´t take any kind of responsibility to the changed contents. this is specialy valid to banners, advertisements or merchandising links in the targeted pages.

|